记录三个MCU外设系统的内部控制单元:WDT,Timer和RTC

1 WDT

1.1 定义

WDT:whatch dog timer。如何证明如果系统正常运作,可以每隔一定的时间执行某一段代码,如果那段代码没有被执行,那么就说明代码或者系统死掉了。可以这么理解,那段要规律执行的代码就是狗,规律的去执行它,就是喂狗的行为,如果一段时间不去喂养,狗就死了,系统也就死了。所以说,WDT是用来监测系统是否正常运转的,如果系统跑飞了,狗死了,WDT就复位一次系统。

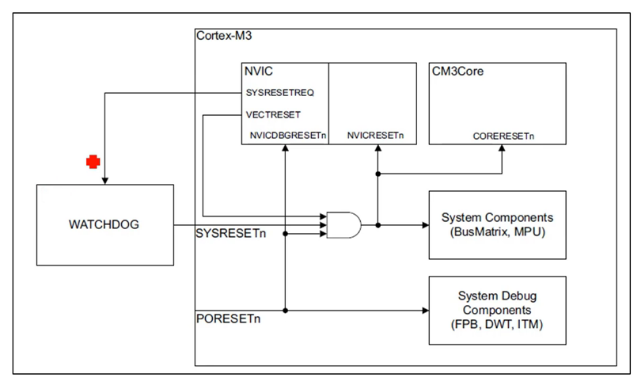

图:WATCHDOG在MCU中的位置

从图中可以看出,WDT复位的有:BVICRESETn,CM3Core和System Components(总线互联矩阵和内存保护单元MPU),但是WDT是不会复位系统调试模块的。

1.2 电路设计

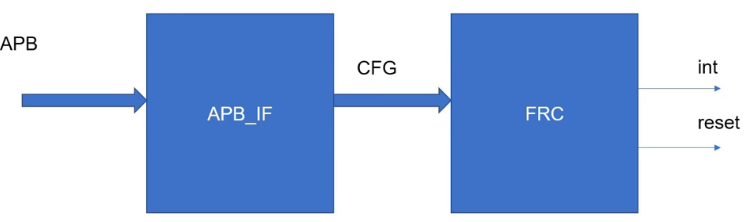

FRC:Free Running Counter,这是一个32位的,自动减一的计数器。

图:Timer的框图结构

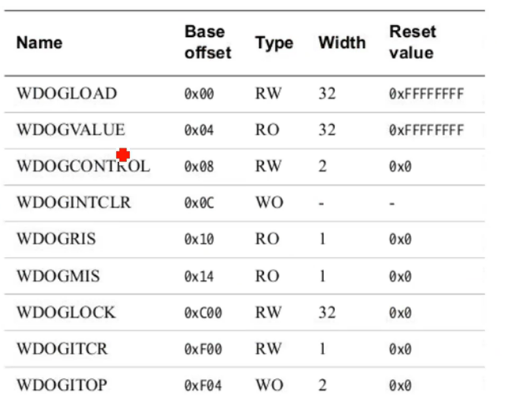

图:寄存器参考分布

WDOGLOAD寄存器:存储一个初始值,之后不断减一,最小值是1;

WDOGVALUE寄存器:上报作用,指示当前值;

WDOGCONTROL寄存器:软件通过控制该寄存器,来控制看门狗的一些功能部件

相关的寄存器设置,可以找一个MCU的寄存器手册,手册基本上可以当做SPEC来参考。

2 WDT的跨时钟域的设计难点

//------------------------------------------------------------------------------// Load enable register//------------------------------------------------------------------------------// The load_en pulse needs to be sampled into the WDOGCLK domain even if PCLK// is subsequently disabled. // load_req_tog_p is toggled if a new load request is received and there are no // pending load requests. This prevents multiple toggles before the next // WDOGCLK edge. assign load_tog_en = load_en_reg & (~load_req_w); // New load request and none pending // load_tog_en high toggles LoadReqTog on next PCLK always @ (negedge PRESETn or posedge PCLK) begin : p_load_req_tog_p_seq if (~PRESETn) load_req_tog_p <= 1'b0; else if (load_tog_en) load_req_tog_p <= (~load_req_tog_p); end // Register LoadReqTog into WDOGCLK domain always @(negedge WDOGRESn or posedge WDOGCLK) begin : p_load_req_tog_w_seq if (~WDOGRESn) load_req_tog_w <= 1'b0; else if (WDOGCLKEN) load_req_tog_w <= load_req_tog_p; end // load_req_w goes high on the PCLK edge after load_tog_en and low on the next // valid WDOGCLK edge assign load_req_w = load_req_tog_p ^ load_req_tog_w;

基本的思路就是,在PCLK的时钟域下,有一个脉冲load_en_reg,根据这个脉冲,定义一个信号load_tog_en,每来一个脉冲,这个load_tog_en信号就取反,这样load_tog_en就是一个持续的翻转信号,翻转频率同脉冲频率。然后,在WDT时钟域下,对这个load_tog_en信号采样,为load_reg_tog_w。这个采样得到的load_reg_tog_w的频率和load_tog_en的频率一样,然后在WDT时钟域下对load_reg_tog_w打一拍处理,然后打拍信号和原信号做异或处理,就可以得到一个在WDT时钟域下的脉冲了。